Page 15 - AB00601_邏輯設計實驗

P. 15

實習 1 基本邏輯閘使用

(3) 消耗電功率(Power dissipated):IC 內所包 V CC

含的每個閘,操作時所需消耗掉的電力,通 I CC

常以毫瓦(mW)為單位,如圖 1-8 所示。

數位電路

靜態功率消耗:P D = V CC × I CC( 平均 ),

其中,I CC( 平均 ) ≡ ( I CC(1) + I CC(0)) / 2。

圖 1-8

(4) 扇出(Fan-out):一個邏輯閘在正常工

作下,其輸出端可接的同族系任何 IC 正常工作

閘的數目,稱為此閘的扇出數,如圖

1-9 所示。簡單的說,在不產生錯誤動 #

作情形下,其所能推動同種類的次級 驅動信號源 N: 驅動個數

閘之數目就稱為「扇出」。

Fan-out = N max 圖 1-9

(5) 扇入(Fan-in):一個邏輯閘輸入端所 m 個

擁有的輸入接腳數目稱為「扇入」, m: 扇入數

如圖 1-10 所示。

圖 1-10

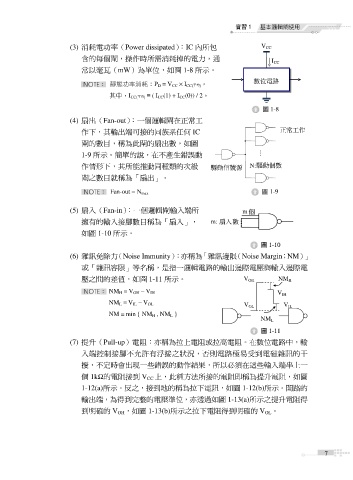

(6) 雜訊免除力(Noise Immunity):亦稱為「雜訊邊限(Noise Margin;NM)」

或「雜訊容限」等名稱,是指一邏輯電路的輸出邊際電壓與輸入邊際電

壓之間的差值,如圖 1-11 所示。 V OH NM H

NM H ≡ V OH − V IH V IH

NM L ≡ V IL − V OL V OL V IL

NM ≡ min { NM H , NM L }

NM L

圖 1-11

(7) 提升(Pull-up)電阻:亦稱為拉上電阻或拉高電阻。在數位電路中,輸

入端控制接腳不允許有浮接之狀況,否則電路極易受到電磁雜訊的干

擾,不定時會出現一些錯誤的動作結果,所以必須在這些輸入端串上一

個 1kΩ的電阻接到 V CC 上,此種方法所接的電阻即稱為提升電阻,如圖

1-12(a)所示。反之,接到地的稱為拉下電阻,如圖 1-12(b)所示。開路的

輸出端,為得到完整的電壓準位,亦透過如圖 1-13(a)所示之提升電阻得

到明確的 V OH,如圖 1-13(b)所示之拉下電阻得到明確的 V OL。

7