Page 17 - AB00601_邏輯設計實驗

P. 17

實習 1 基本邏輯閘使用

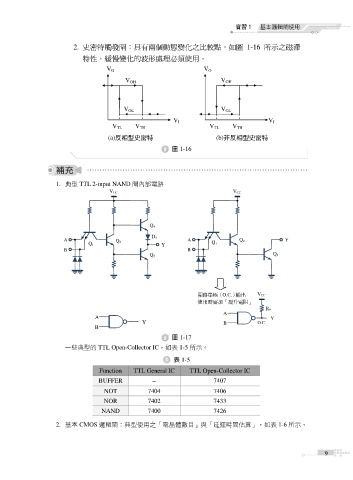

2. 史密特觸發閘:具有兩個動態變化之比較點,如圖 1-16 所示之磁滯

特性,緩慢變化的波形處理必須使用。

V O V O

V OH V OH

V OL V OL

V I V I

V TL V TH V TL V TH

(a)反相型史密特 (b)非反相型史密特

圖 1-16

……………………………………………………………………………

1. 典型 TTL 2-input NAND 閘內部電路

V CC V CC

Q 4

A Q 2 D 5 A Q 2 Y

Q 1 Y Q 1

B B

Q 3 Q 3

開路集極(O.C.) 輸出 V CC

使用時需加「提升電阻」

R P

A

A Y

Y B O.C.

B

圖 1-17

一些典型的 TTL Open-Collector IC,如表 1-5 所示。

表 1-5

Function TTL General IC TTL Open-Collector IC

BUFFER − 7407

NOT 7404 7406

NOR 7402 7433

NAND 7400 7426

2. 基本 CMOS 邏輯閘:典型使用之「電晶體數目」與「延遲時間估算」,如表 1-6 所示。

9