Page 14 - AB00601_邏輯設計實驗

P. 14

邏輯設計實驗

電氣特性與額定值

對於各種積體電路的特性,必須徹底瞭解,因為各種族、類之間的連結,

由於電壓和電流之間高低大小的不同,在連結上需考慮許多因素,以避免問題

電路發生。

幾個在 IC 資料手冊中常見的電氣特性名詞:

1. 邏輯準位(Logic Level):V OH,V OL,V IL,V IH,如圖 1-5 所示。

V O dV O

V OH =−1

dV I

數位電路 V O

V I

V OL

V I

V IL V IH

圖 1-5

2. 操作速度(Operation Speed):指邏輯閘之交換速度(Switching Speed)

(1) 傳輸延遲時間(Propagation Delay time):當信號從一個閘通過時需要一

段時間,這段時間就稱為傳輸延遲時間,如圖 1-6 所示。但對數位電路

而言,其傳輸延遲時間並不為所有閘的延遲時間之和,而是等於一個閘

的延遲時間乘上級數。

V I

V I (1)

50% 50%

V I (0)

V OH V O

50% 50%

V OL

t PHL t PLH

t PHL = time of [(ΔV I (50%)~ΔV O (50%))];When V OH→V OL

t PLH = time of [(ΔV I (50%)~ΔV O (50%))];When V OL→V OH

圖 1-6

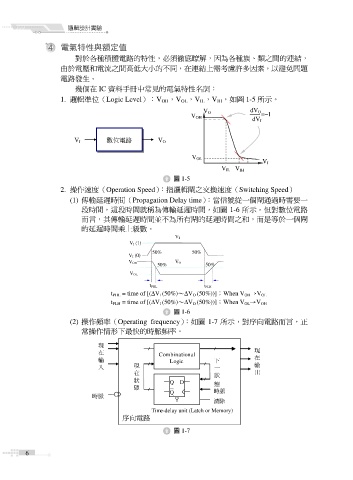

(2) 操作頻率(Operating frequency):如圖 1-7 所示,對序向電路而言,正

常操作情形下最快的時脈頻率。

現

在 Combinational 現

輸 Logic 下 在

入 現 一 輸

在 出

狀

狀 Q D

態 態

Q 時脈

時脈

清除

Time-delay unit (Latch or Memory)

序向電路

圖 1-7

6