Page 14 - eAB03001_數位電路實作應用_課本PDF

P. 14

CPLD 數位邏輯設計實習

2 ISP 下載電路

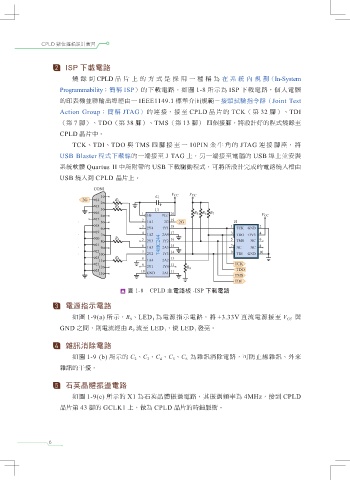

燒錄到 CPLD 晶片上的方式是採用一種稱為 在系統內規劃(In-System

Programmability;簡稱 ISP)的下載電路。如圖 1-8 所示為 ISP 下載電路,個人電腦

的印表機並聯輸出埠經由一 IEEE1149.1 標準介面規範-接頭試驗指令群(Joint Test

Action Group; 簡稱 JTAG) 的連接, 接至 CPLD 晶片的 TCK( 第 32 腳 )、TDI

(第 7 腳)、TDO(第 38 腳)、TMS(第 13 腳) 四個接腳,將設計好的程式燒錄至

CPLD 晶片中。

TCK、TDI、TDO 與 TMS 四腳接至一 10PIN 金牛角的 JTAG 連接腳座, 將

USB Blaster 程式下載線的一端接至 J TAG 上,另一端接至電腦的 USB 埠上並安裝

系統軟體 Quartus II 中所附帶的 USB 下載驅動程式,可將所設計完成的電路燒入檔由

USB 燒入到 CPLD 晶片上。

圖 1-8 CPLD 主電路板 -ISP 下載電路

3 電源指示電路

如圖 1-9(a) 所示,R 、LED 為電源指示電路,將 +3.33V 直流電源接至 V 與

9

1

CC

GND 之間,則電流經由 R 流至 LED ,使 LED 發亮。

1

9

1

4 雜訊消除電路

如圖 1-9 (b) 所示的 C 、C 、C 、C 、C 為雜訊消除電路,可防止線雜訊、外來

3

4

5

6

2

雜訊的干擾。

5 石英晶體振盪電路

如圖 1-9(c) 所示的 X1 為石英晶體振盪電路,其振盪頻率為 4MHz,接到 CPLD

晶片第 43 腳的 GCLK1 上,做為 CPLD 晶片的時鐘脈衝。

6