Page 12 - eAB03001_數位電路實作應用_課本PDF

P. 12

CPLD 數位邏輯設計實習

2 可規劃互連陣列(Programmable Interconnect Array;簡稱 PIA)

可規劃互連陣列(PIA) 負責信號的傳遞, 如圖 1-3 所示的可規劃互連陣列

(PIA)佈線圖看出,信號藉由可規劃選擇開關連接至所有的巨集晶胞。

圖 1-3 可規劃互連陣列(PIA)佈線圖

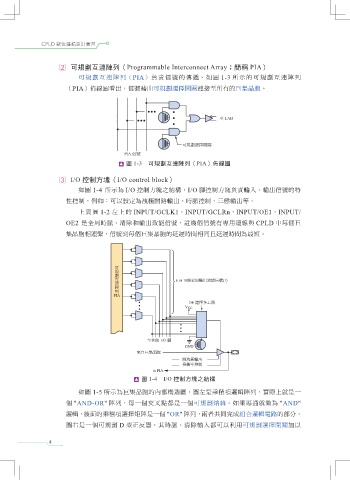

3 I/O 控制方塊(I/O control block)

如圖 1-4 所示為 I/O 控制方塊之結構,I/O 腳控制方塊負責輸入、輸出信號的特

性控制,例如:可以設定為洩極開路輸出、時脈控制、三態輸出等。

上頁圖 1-2 左上的 INPUT/GCLK1,INPUT/GCLRn,INPUT/OE1,INPUT/

OE2 是全局時脈、清除和輸出致能信號,這幾個信號有專用連線與 CPLD 中每個巨

集晶胞相連繫,信號到每個巨集晶胞的延遲時間相同且延遲時間為最短。

圖 1-4 I/O 控制方塊之結構

如圖 1-5 所示為巨集晶胞的內部構造圖,圖左是乘積項邏輯陣列,實際上就是一

個 "AND-OR" 陣列,每一個交叉點都是一個可規劃熔絲。如果導通就做為 "AND"

邏輯,後面的乘積項選擇矩陣是一個 "OR" 陣列,兩者共同完成組合邏輯電路的部分。

圖右是一個可規劃 D 型正反器,其時脈、清除輸入都可以利用可規劃選擇開關加以

4