Page 13 - eAB03001_數位電路實作應用_課本PDF

P. 13

數位邏輯實驗開發系統介紹 Chapter 1

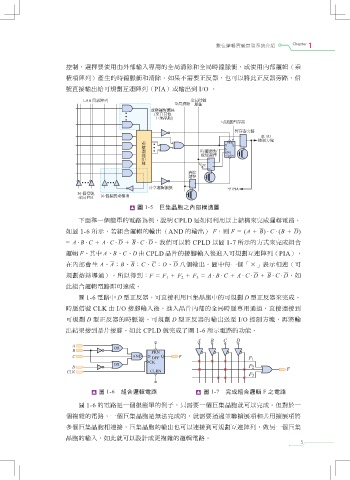

控制,選擇要使用由外部輸入專用的全局清除和全局時鐘脈衝,或使用內部邏輯(乘

積項陣列)產 生的時鐘脈衝和清除。如果不需要正反器,也可以將此正反器旁路,信

號直接輸出給可規劃互連陣列(PIA)或輸出到 I/O 。

圖 1-5 巨集晶胞之內部構造圖

下面舉一個簡單的電路 為例,說明 CPLD 是如何利用以上結構來完成邏輯電路,

如圖 1-6 所示,若組合邏輯的輸出(AND 的輸出) F,則 F = (A + B) · C · (B + D)

= A · B · C + A · C · D + B · C · D。我們可以將 CPLD 以圖 1-7 所示的方式來完成組合

邏輯 F。其中 A、B、C、D 由 CPLD 晶片的接 腳輸入後進入可規劃互連 陣列(PIA),

在內部會 生 A、A;B、B;C、C;D、D 八個輸出。圖中每一個「×」表示相連(可

規劃熔絲導通),所以得到:F = F + F + F = A · B · C + A · C · D + B · C · D,如

3

2

1

此組合邏輯電路即可達成。

圖 1-6 電路中 D 型正反器,可直接利用巨集晶胞中的可規劃 D 型正反器來完成。

時脈信號 CLK 由 I/O 接腳輸入後,進入晶片內部的全局時脈專用通道,直接連接到

可規劃 D 型正反器的時脈端。可規劃 D 型正反器的輸出送至 I/O 控制方塊,再將輸

出結果接到晶片接腳。如此 CPLD 就完成了圖 1-6 所示電路的功能。

圖 1-6 組合邏輯電路 圖 1-7 完成組合邏輯 F 之電路

圖 1-6 的電路是一個很簡單的例子,只需要一個巨集晶胞就可以完成。但對於一

個複雜的電路,一個巨集晶胞是無法完成的,就需要通過並聯擴展項和共用擴展項將

多個巨集晶胞相連接,巨集晶胞的輸出也可以連接到可規劃互連陣列,做 另一個巨集

晶胞的輸入,如此就可以設計成更複雜的邏輯電路。

5