Page 30 - eAC21710_可程式邏輯設計(全)_課本PDF

P. 30

可程式邏輯設計實習

(3) 可規劃行 / 列快速追蹤交互連線

若設計一個較大的數位邏輯電路,可能需要用到數個 LAB,此時 LAB 與

LAB 之間就必須透過可規劃行 / 列快速追蹤交互連線(Column/Row Fast Track

Interconnect)的聯繫。

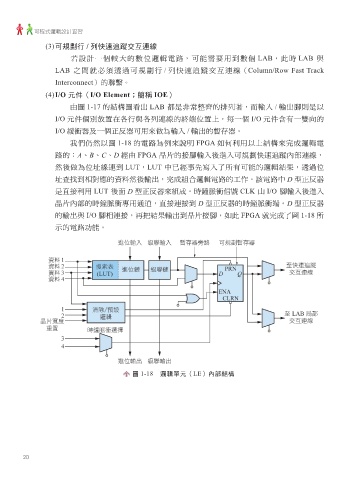

(4) I/O 元件(I/O Element;簡稱 IOE)

由圖 1-17 的結構圖看出 LAB 都是非常整齊的排列著,而輸入 / 輸出腳則是以

I/O 元件個別放置在各行與各列連線的終端位置上,每一個 I/O 元件含有一雙向的

I/O 緩衝器及一個正反器可用來做為輸入 / 輸出的暫存器。

我們仍然以圖 1-18 的電路為例來說明 FPGA 如何利用以上結構來完成邏輯電

路的:A、B、C、D 經由 FPGA 晶片的接腳輸入後進入可規劃快速追蹤內部連線,

然後做為位址線連到 LUT,LUT 中已經事先寫入了所有可能的邏輯結果,透過位

址查找到相對應的資料然後輸出,完成組合邏輯電路的工作。該電路中 D 型正反器

是直接利用 LUT 後面 D 型正反器來組成。時鐘脈衝信號 CLK 由 I/O 腳輸入後進入

晶片內部的時鐘脈衝專用通道,直接連接到 D 型正反器的時鐘脈衝端。D 型正反器

的輸出與 I/O 腳相連接,再把結果輸出到晶片接腳,如此 FPGA 就完成了圖 1-18 所

示的電路功能。

圖 1-18 邏輯單元(LE)內部結構

20

"$ @$) JOEE ɪʹ