Page 27 - eAC21710_可程式邏輯設計(全)_課本PDF

P. 27

Chapter 1

工場安全衛生及邏輯設計應用

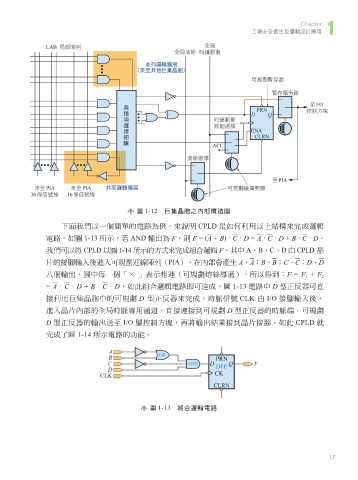

圖 1-12 巨集晶胞之內部構造圖

下面我們以一個簡單的電路為例,來說明 CPLD 是如何利用以上結構來完成邏輯

電路。如圖 1-13 所示,若 AND 輸出為 F,則 F = (A + B) · C · D = A · C · D + B · C · D。

我們可以將 CPLD 以圖 1-14 所示的方式來完成組合邏輯 F。其中 A、B、C、D 由 CPLD 晶

片的接腳輸入後進入可規劃連線陣列(PIA),在內部會產生 A、A;B、B;C、C;D、D

八個輸出。圖中每一個「× 」表示相連(可規劃熔絲導通),所以得到:F = F + F

2

1

= A · C · D + B · C · D,如此組合邏輯電路即可達成。圖 1-13 電路中 D 型正反器可直

接利用巨集晶胞中的可規劃 D 型正反器來完成。時脈信號 CLK 由 I/O 接腳輸入後,

進入晶片內部的全局時脈專用通道,直接連接到可規劃 D 型正反器的時脈端。可規劃

D 型正反器的輸出送至 I/O 腳控制方塊,再將輸出結果接到晶片接腳。如此 CPLD 就

完成了圖 1-14 所示電路的功能。

圖 1-13 組合邏輯電路

17

"$ @$) JOEE ɪʹ