Page 22 - 數位邏輯設計升學寶典

P. 22

14 數位邏輯設計

110 年四技

第 2 頁 公告試題僅供參考 答對率 出題年度

難易度

電機與電子群資電類

共 12 頁 Chapter 1 歷屆統測精選 專業科目(二)

易 中 難 40% 109

第一部份:數位邏輯(第 1 至 13 題,每題 2 分,共 26 分)

ˉ

1. ݔɓಂᅰЗڦٙتҖνྡהͪd࿁༈ಂᅰЗڦdɨΐાࠑО٫͍ᆽk

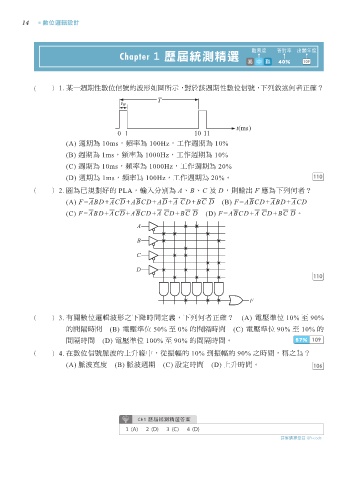

1. 某一週期性數位信號的波形如圖(一)所示,對於該週期性數位信號,下列敘述何者正確?

T

t W

t(ms)

圖(一) 0 1 10 11

1

(A) 週期為10ms,頻率為100Hz,工作週期為10%

(A) ಂމ 10msd᎖ଟމ 100HzdʈЪಂމ 10%

(B) 週期為1ms,頻率為1000Hz,工作週期為10%

(B) ಂމ 1msd᎖ଟމ 1000HzdʈЪಂމ 10%

(C) 週期為10ms,頻率為1000Hz,工作週期為20%

(C) ಂމ 10msd᎖ଟމ 1000HzdʈЪಂމ 20%

(D) 週期為1ms,頻率為100Hz,工作週期為20%

ˉ (D) ಂމ 1msd᎖ଟމ 100HzdʈЪಂމ 20%f 110

2. 使用8位元表示的十六進制2A (16)數值,經由2的補數(2's Complements)運算後,其數值為何?

2. ྡމʊྌλٙ PLAd፩ɝʱйމ AeBeC ʿ Ddۆ፩̈ F ᏐމɨΐО٫k

(A) D3 (16) (B) D4 (16) (C) D5 (16) (D) D6 (16)

ˉ (A) F=ABD+ACD+ABCD+AD+A CD+BC Dc(B) F=ABCD+ABD+ACD

3. 布林代數表示式 X (A+B)(C+D) 使用第摩根定理簡化後的輸出為何?

(C) F=ABD+ACD+ABCD+A CD+BC Dc(D) F=ABCD+A CD+BC Df

(A) X=ABCD (B) X=AB+CD (C) X=AB+CD (D) X=AB+CD

ˉ

4. 圖(二)為某JK型正反器的接線圖,時脈輸入(CLK)為 10kHz方波,Q的初始狀態為0,則

CLK A與CLK B的輸出波形,下列何者正確?

HIGH

J Q CLK A

CLK CK 110

K Q CLK B

圖(二)

CLK CLK

3. ϞᗫᅰЗᜌ፨تҖʘɨࠥࣛග່֛dɨΐО٫͍ᆽk (A) ཥᏀЗ 10% Ї 90%

(A) CLK A (B) CLK A

ٙගཞࣛගc(B) ཥᏀЗ 50% Ї 0% ٙගཞࣛගc(C) ཥᏀЗ 90% Ї 10% ٙ

CLK B CLK B

ගཞࣛගc(D) ཥᏀЗ 100% Ї 90% ٙගཞࣛගf 57% 109

CLK CLK

4. ίᅰЗڦএتٙɪʺᇝʕdࣈషٙ 10% Ցࣈషٙ 90% ʘࣛගd၈ʘމk

(C) CLK A (D) CLK A 106

(A) এتᄱܓc(B) এتಂc(C) ண֛ࣛගc(D) ɪʺࣛගf

CLK B CLK B

ˉ

5. 圖(三)為一組合邏輯電路,經化簡後的最簡布林函數,下列何者正確?

(A) Y=ABC+CD

(B) Y=ABC+AB A

B

Ch1 歷屆統測精選答案 Y

(C) Y=ACD+AB 1 (A) 2 (D) 3 (C) 4 (D) C

D

圖(三)

(D) Y=ACD+CD 1 詳解請掃章首 QR-code

1 1

ˉ

6. 欲把 16 個 1 位元的資料用 16 個時脈週期暫存到 1 個 16 位元的移位暫存器,再用 1 個時脈

週期傳給 1 個 16 位元的微控制器來處理,則需要用到下列哪種移位暫存器?

(A) SISO(Serial In Serial Out) (B) SIPO(Serial In Parallel Out)

(C) PISO(Parallel In Serial Out) (D) PIPO(Parallel In Parallel Out)

-2-