Page 29 - AC21310_電子書PDF

P. 29

101010110001100101010110101010101010111010111111100000110011100001110001111000010101010

001110100101010101100011001010101101010101010101110101111111000001100111000011100011110

00010101010001110100101010101100011001010101101010101010101110101111111000001100111000

011100011110000101010100011101001010101011000110010101011010101010101011101011111110000

01100111000011100011110000101010100011101001010101011000110010101011010101010101011101

數位邏輯設計 全一冊

011111110000011001110000111000111100001010101000111010010101010110001100101010110101010

101010111010111111100000110011100001110001111000010101010001110100101010101100011001010

學習重點回顧

101101010101010101110101111111000001100111000011100011110000101010100011101001010101011

000110010101011010101010101011101011111110000011001110000111000111100001010101000111010

010101010110001100101010110101010101010111010111111100000110011100001110001111000010101

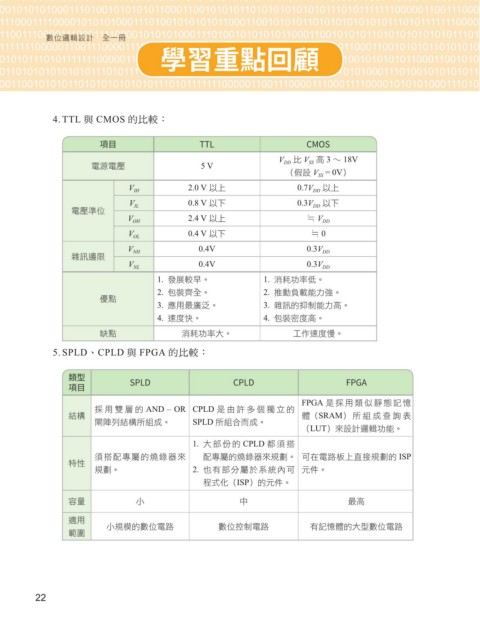

4. TTL 與 CMOS 的比較:

項目 TTL CMOS

V 比 V 高 3 ~ 18V

電源電壓 5 V DD SS

(假設 V = 0V)

SS

V IH 2.0 V 以上 0.7V DD 以上

V IL 0.8 V 以下 0.3V DD 以下

電壓準位

V OH 2.4 V 以上 ≒ V DD

V OL 0.4 V 以下 ≒ 0

V NH 0.4V 0.3V DD

雜訊邊限

V NL 0.4V 0.3V DD

1. 發展較早。 1. 消耗功率低。

2. 包裝齊全。 2. 推動負載能力強。

優點

3. 應用最廣泛。 3. 雜訊的抑制能力高。

4. 速度快。 4. 包裝密度高。

缺點 消耗功率大。 工作速度慢。

5. SPLD、CPLD 與 FPGA 的比較:

類型

SPLD CPLD FPGA

項目

FPGA 是採用類似靜態記憶

採用雙層的 AND – OR CPLD 是由許多個獨立的

結構 體(SRAM)所組成查詢表

閘陣列結構所組成。 SPLD 所組合而成。

(LUT)來設計邏輯功能。

1. 大部份的 CPLD 都須搭

須搭配專屬的燒錄器來 配專屬的燒錄器來規劃。 可在電路板上直接規劃的 ISP

特性

規劃。 2. 也有部分屬於系統內可 元件。

程式化(ISP)的元件。

容量 小 中 最高

適用

小規模的數位電路 數位控制電路 有記憶體的大型數位電路

範圍

22

"$ @$) JOEE ɪʹ