Page 26 - AC21310_電子書PDF

P. 26

數位邏輯基本概念1

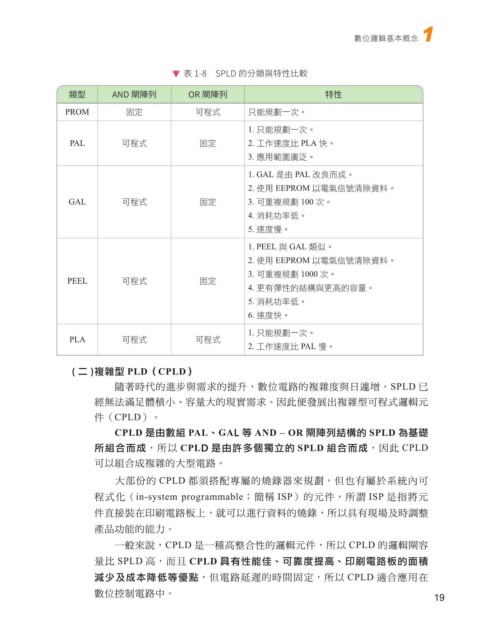

表 1-8 SPLD 的分類與特性比較

類型 AND 閘陣列 OR 閘陣列 特性

PROM 固定 可程式 只能規劃一次。

1. 只能規劃一次。

PAL 可程式 固定 2. 工作速度比 PLA 快。

3. 應用範圍廣泛。

1. GAL 是由 PAL 改良而成。

2. 使用 EEPROM 以電氣信號清除資料。

GAL 可程式 固定 3. 可重複規劃 100 次。

4. 消耗功率低。

5. 速度慢。

1. PEEL 與 GAL 類似。

2. 使用 EEPROM 以電氣信號清除資料。

3. 可重複規劃 1000 次。

PEEL 可程式 固定

4. 更有彈性的結構與更高的容量。

5. 消耗功率低。

6. 速度快。

1. 只能規劃一次。

PLA 可程式 可程式

2. 工作速度比 PAL 慢。

( 二 ) 複雜型 PLD(CPLD)

隨著時代的進步與需求的提升,數位電路的複雜度與日遽增,SPLD 已

經無法滿足體積小、容量大的現實需求。因此便發展出複雜型可程式邏輯元

件(CPLD)。

CPLD 是由數組 PAL、GAL 等 AND – OR 閘陣列結構的 SPLD 為基礎

所組合而成,所以 CPLD 是由許多個獨立的 SPLD 組合而成,因此 CPLD

可以組合成複雜的大型電路。

大部份的 CPLD 都須搭配專屬的燒錄器來規劃,但也有屬於系統內可

程式化(in-system programmable;簡稱 ISP)的元件,所謂 ISP 是指將元

件直接裝在印刷電路板上,就可以進行資料的燒錄,所以具有現場及時調整

產品功能的能力。

一般來說,CPLD 是一種高整合性的邏輯元件,所以 CPLD 的邏輯閘容

量比 SPLD 高,而且 CPLD 具有性能佳、可靠度提高、印刷電路板的面積

減少及成本降低等優點,但電路延遲的時間固定,所以 CPLD 適合應用在

數位控制電路中。 19

"$ @$) JOEE ɪʹ