Page 19 - AC21310_電子書PDF

P. 19

數位邏輯設計 全一冊

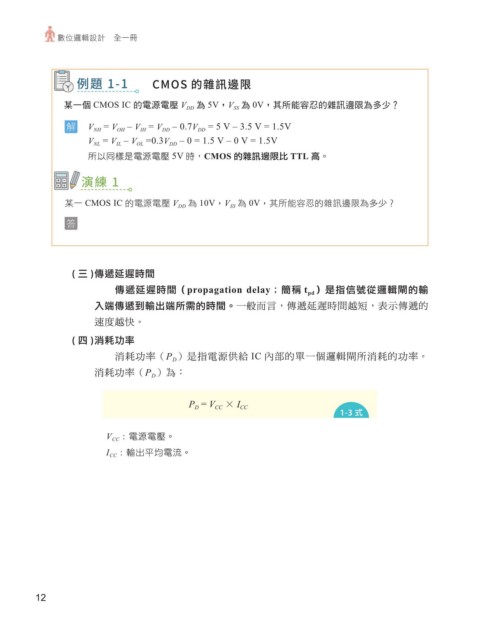

例題 1-1 CMOS 的雜訊邊限

某一個 CMOS IC 的電源電壓 V DD 為 5V,V 為 0V,其所能容忍的雜訊邊限為多少?

SS

解 V = V – V = V – 0.7V = 5 V – 3.5 V = 1.5V

DD

NH

IH

OH

DD

V = V – V =0.3V – 0 = 1.5 V – 0 V = 1.5V

DD

OL

IL

NL

所以同樣是電源電壓 5V 時,CMOS 的雜訊邊限比 TTL 高。

演練 1

某一 CMOS IC 的電源電壓 V DD 為 10V,V 為 0V,其所能容忍的雜訊邊限為多少?

SS

答

( 三 ) 傳遞延遲時間

傳遞延遲時間(propagation delay;簡稱 t )是指信號從邏輯閘的輸

pd

入端傳遞到輸出端所需的時間。一般而言,傳遞延遲時間越短,表示傳遞的

速度越快。

( 四 ) 消耗功率

消耗功率(P )是指電源供給 IC 內部的單一個邏輯閘所消耗的功率。

D

消耗功率(P )為:

D

P = V × I CC

D

CC

1-3 式

V :電源電壓。

CC

I :輸出平均電流。

CC

12

"$ @$) JOEE ɪʹ