Page 18 - AC21310_電子書PDF

P. 18

數位邏輯基本概念1

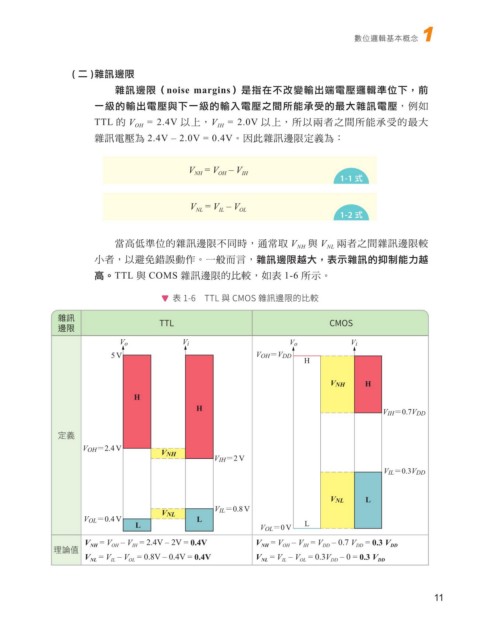

( 二 ) 雜訊邊限

雜訊邊限(noise margins)是指在不改變輸出端電壓邏輯準位下,前

一級的輸出電壓與下一級的輸入電壓之間所能承受的最大雜訊電壓,例如

TTL 的 V = 2.4V 以上,V = 2.0V 以上,所以兩者之間所能承受的最大

IH

OH

雜訊電壓為 2.4V – 2.0V = 0.4V。因此雜訊邊限定義為:

V = V – V IH

NH

OH

1-1 式

V = V – V OL

NL

IL

1-2 式

當高低準位的雜訊邊限不同時,通常取 V NH 與 V NL 兩者之間雜訊邊限較

小者,以避免錯誤動作。一般而言,雜訊邊限越大,表示雜訊的抑制能力越

高。TTL 與 COMS 雜訊邊限的比較,如表 1-6 所示。

表 1-6 TTL 與 CMOS 雜訊邊限的比較

雜訊

TTL CMOS

邊限

定義

V = V – V = 2.4V – 2V = 0.4V V = V – V = V – 0.7 V = 0.3 V DD

IH

IH

OH

NH

NH

DD

DD

OH

理論值

V = V – V = 0.8V – 0.4V = 0.4V V = V – V = 0.3V – 0 = 0.3 V DD

NL

IL

OL

DD

NL

IL

OL

11

"$ @$) JOEE ɪʹ